科技日報記者 張佳欣

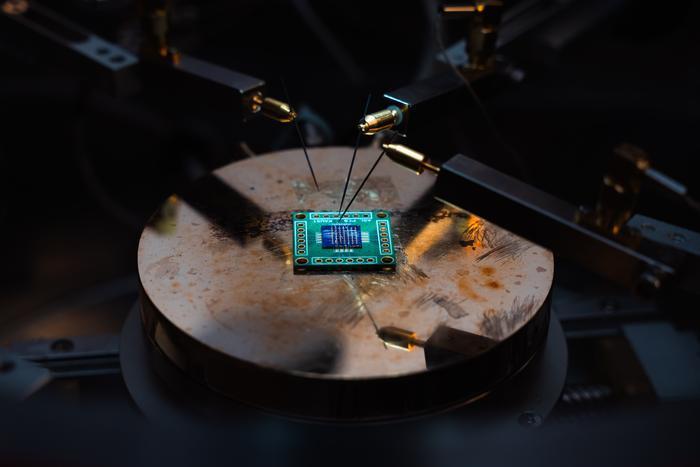

沙特阿卜杜拉國王科技大學研究人員在微芯片設計領域創下新紀錄,成功研制出全球首個面向大面積電子器件的6層堆疊式混合互補金屬氧化物半導體(CMOS)芯片。此前公開報道的混合CMOS堆疊層數從未超過兩層,這一突破標志著芯片集成密度與能效邁上新臺階,為電子設備的小型化和性能提升開辟了新方向。

CMOS芯片幾乎存在于所有電子設備中,從手機、電視到衛星和醫療儀器。與傳統硅基芯片相比,混合CMOS芯片在大面積電子領域更具優勢,有望在柔性電子、智慧醫療和物聯網等領域發揮重要作用。

長期以來,半導體行業一直依靠縮小晶體管尺寸來提高集成密度,但已接近量子力學的極限,同時成本也在急劇上升。要繼續推進芯片性能,必須走出平面擴展的思路,垂直堆疊晶體管是最具潛力的方向之一。

芯片多層堆疊的最大挑戰在于制造溫度。常規工藝往往需要幾百攝氏度的高溫,這在添加新層時可能會損壞下層結構。而新方法中,所有工藝步驟的溫度均未超過150℃,多數步驟甚至接近室溫完成,顯著降低了材料受損風險。

此外,層與層之間的表面必須盡可能光滑。新設計中改進了工藝,使表面平整度優于以往。而在垂直堆疊中,層間精確對準尤為重要,研究團隊也在這方面顯著優化了制造流程。

在微芯片設計中,核心目標就是在更小的空間里實現更高性能。此次研究通過優化多個關鍵步驟,為垂直擴展與功能密度的進一步提升提供了一條可行路徑。

總編輯圈點

科研人員建成了全球首個擁有6層功能電路的微縮芯片“摩天大樓”,可以在同樣“占地面積”的地基上,通過加高“樓層”讓芯片容納更多晶體管,實現更精妙復雜的功能。一直以來,半導體行業致力于縮小晶體管尺寸,以在方寸之間排布更多晶體管,但這種方式已越發難以為繼。此次,科研人員改進了制造工藝,攻克了芯片多層堆疊的兩大核心挑戰——溫度和平滑度,成功實現“平地起高樓”,為芯片進一步提升性能開辟了新的路徑和方向。